1.SPI接(jiē)口原理

串行外围设备接口(Serial Peripheral Interface,SPI),用来在微控制器和(hé)外围设备芯片(piàn)之间提供一(yī)个低成本(běn)、易使(shǐ)用的接口(SPI有时候也被称为4线接口)。这种接(jiē)口可以用来连(lián)接存储器(存储(chǔ)数据(jù))、A/D转换(huàn)器、D/A转(zhuǎn)换器、实时时钟(zhōng)日历、LCD驱动器(qì)、传感(gǎn)器等等。

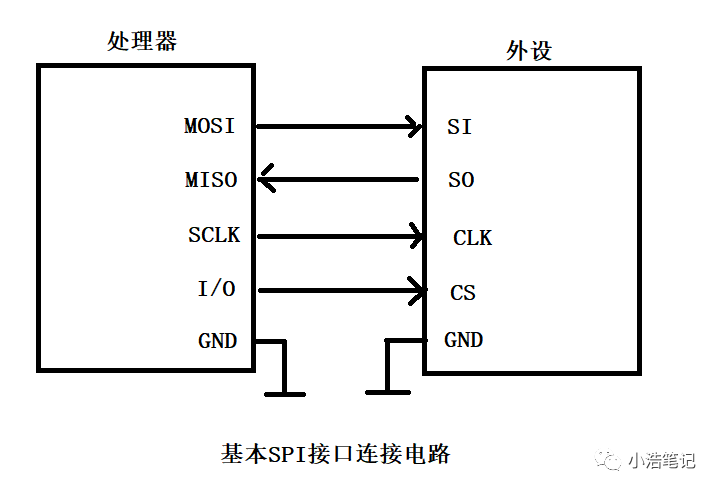

SPI主要使用四(sì)个信号:主(zhǔ)机输出/从机输入(MOSI)、主机(jī)输入/从机(jī)输出(MISO)、串行SCLK或SCK、外设芯片(CS)。有些处理器有(yǒu)SPI接口(kǒu)专用的芯片选(xuǎn)择(zé),称为从机选择(zé)SS。

MOSI信号由主机产生,从机(jī)接受。在有些芯(xīn)片上,MOSI只被(bèi)简单地标为串行输(shū)入(rù)(SI),或者串行数据输入SDI。MISO信号由从(cóng)机产(chǎn)生,不过还是在(zài)主机(jī)的(de)控制下产生(shēng)的。在(zài)一些芯片上,MISO有时被称(chēng)为串行输出(SO),或(huò)者串行数据输出(SDO)。外设片选信号(hào)通常只是由(yóu)主机的备用(yòng)I/O引脚产生。

与(yǔ)标准的(de)串行(háng)接口接(jiē)口不同,SPI是一个同步协议(yì)接口(kǒu),所有的传输都参照(zhào)一个共同的时(shí)钟,这个同(tóng)步时(shí)钟信号由主(zhǔ)机产生,接收数据的外设使用时钟来(lái)对串行比特流的接受进行同步化。可以(yǐ)将多个具(jù)有SPI接口的芯片连到主机的同一个SPI接口上,主机通过(guò)控制从设备(bèi)的片选(xuǎn)输入引脚来选择接受数(shù)据(jù)的从设备。

2.SPI传(chuán)输过程

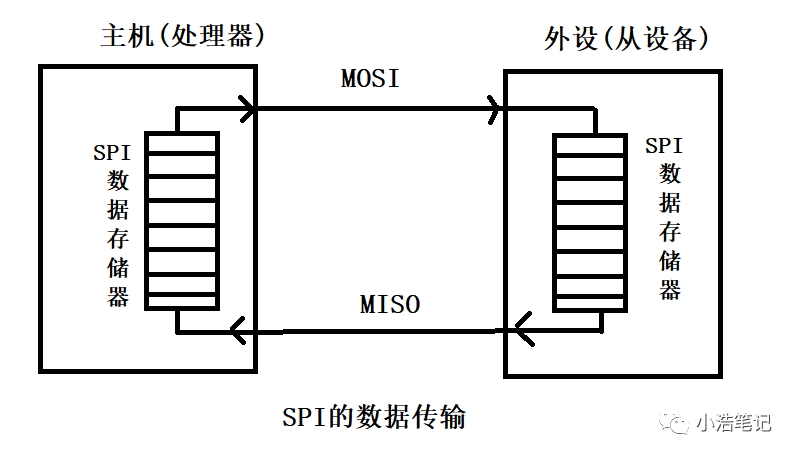

主机和外设都包含一(yī)个串(chuàn)行(háng)移位寄存器,主机通过(guò)它(tā)的SPI串行(háng)寄存器写入一个字(zì)节来发起一次(cì)传(chuán)输。寄存器是通过(guò)MOSI信号线将字节传送给外(wài)设,外设也将(jiāng)自己的(de)移位寄存器中的内容通过(guò)MISO信(xìn)号线返回(huí)给主机。这样,两(liǎng)个(gè)移位寄存器中的内容(róng)就(jiù)被交换了(le)。外(wài)设的写操作和(hé)读操作是同步完成的,因此SPI成为一个很有效的(de)协议。

如果只是进(jìn)行写操作(zuò),主机只需忽略收到的(de)字节;反过来,如果主(zhǔ)机(jī)要读取外设的一个字(zì)节,就必须发送(sòng)一个空字节来引发从机的传输。

当主机发送一个连续(xù)的数据流时(shí),有些外设能够进行(háng)多字(zì)节传输。许多拥有(yǒu)SPI接口的存(cún)储器(qì)芯片都以这种方(fāng)式工作。在这种传(chuán)输方式(shì)下,SPI外设的芯片选择端必(bì)须在整个(gè)传(chuán)输(shū)过程中(zhōng)保持低电平(píng)。比如,存储器芯片会希(xī)望(wàng)在一个“写“命(mìng)令之后紧接着收到的是四个地(dì)址字节(起始地(dì)址),这(zhè)样,后面接受到的数(shù)据就可以存储到(dào)该地址(zhǐ)。一次传输可(kě)能会涉及千字节的移(yí)位或更多信息。

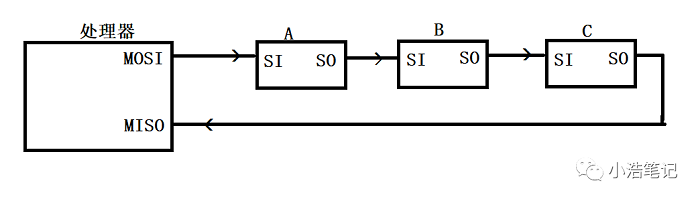

其(qí)他(tā)外设只需(xū)要一个单字节(比如(rú)一个发给A/D转换器的命令),有(yǒu)些甚至还支持菊花链连接(jiē),菊花链(liàn)连(lián)接三台SPI设备,如下图:

主机处(chù)理(lǐ)器从其SPI接口发送三个字节(jiē)的数据。第一个字节(jiē)发送(sòng)给外设A,当(dāng)第二个字节发送给外设A的时候,第一个字节已移出了A,而(ér)传送给(gěi)了B。同样,主机想要从外(wài)设(shè)A读取一个(gè)结果(guǒ),它必须(xū)再(zài)发送一个3字节(空字节)的序列,这样(yàng)就(jiù)可以把A中的数据(jù)移到B中,然后再移到(dào)C中,最后送回(huí)到(dào)主机。在这个过程(chéng)中,主机还(hái)依次从B和(hé)C接受到字节。

注意,菊花链连接不一定适(shì)用于所有的SPI设备,特(tè)别(bié)是要求多字节传输的设备(比如存储器芯(xīn)片),有(yǒu)的外设芯片也不支持菊花链连接。

根(gēn)据时钟极性和时钟相位的不同(tóng),SPI有(yǒu)四(sì)个工作模式:

时钟极(jí)性(xìng)CPOL有(yǒu)高、低两(liǎng)极;时钟极性为(wéi)低(dī)电平(píng)时,空闲时时钟(SCK)处(chù)于低电平,传输时(shí)跳到高电平;时钟极性为高电平时,空闲时(shí)时钟(zhōng)处(chù)于高电平,传输时跳到低(dī)电(diàn)平。

时钟相(xiàng)位(wèi)CPHA有两个:时钟(zhōng)相(xiàng)位0和时钟相位1。当时钟相位为0时,时(shí)钟(zhōng)周(zhōu)期的前一边缘采集(jí)数据;当时钟相位为1时,时钟周期(qī)的后一边缘采集数(shù)据。

客服QQ1:63355785 客服QQ2:61303373 客(kè)服QQ3:67399965 客服QQ4:2656068273 产(chǎn)品分类地(dì)图

版(bǎn)权所有:保定市leyu.乐鱼和禾邦电子有限公(gōng)司 保定市(shì)leyu.乐鱼和禾邦电子有限公司(sī)营业执照

关键字:保定电子元器(qì)件 保定电子元件 电(diàn)子元器件 电(diàn)子元件